5.1. CPU High and Peripherals¶

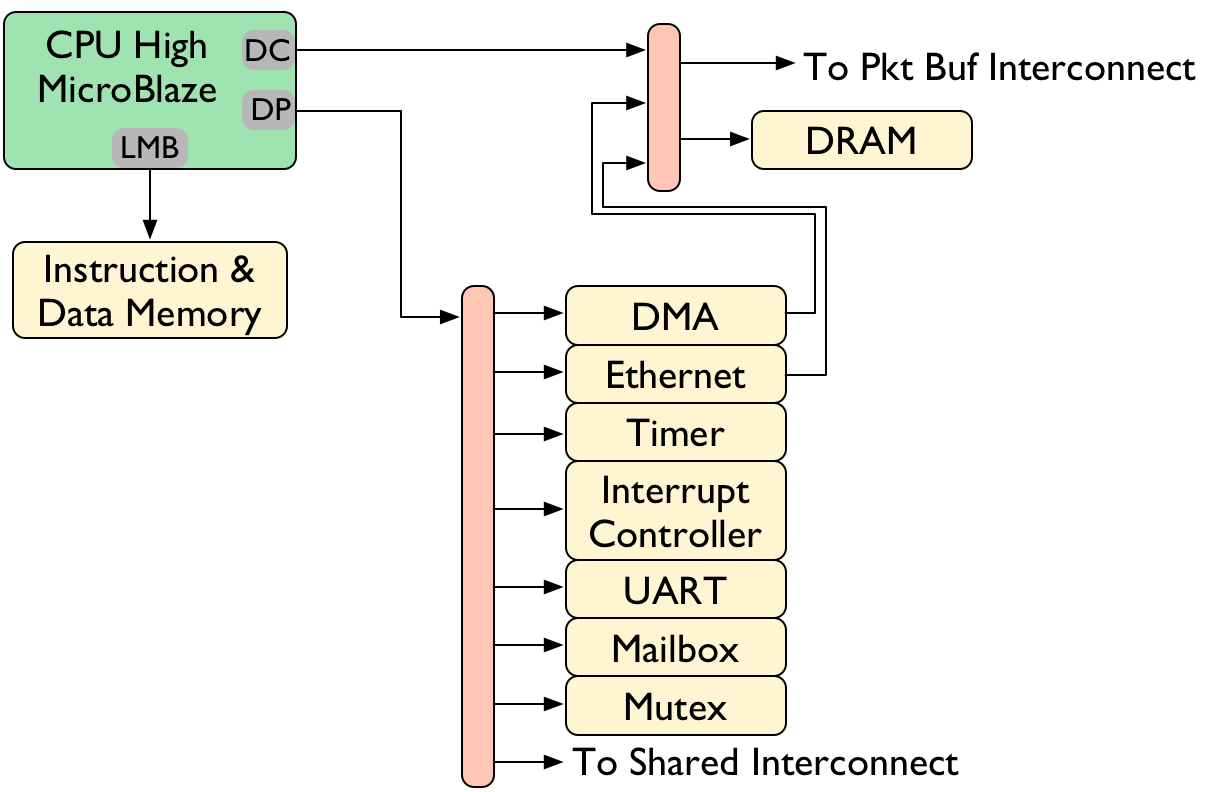

CPU High is the MicroBlaze CPU dedicated to high-level MAC operations.

The CPU High MicroBlaze core has two AXI master interfaces:

- DP: Peripheral data interface, 32-bit AXI master

- DC: Cached data interface, 64-bit AXI master

The MicroBlaze is configured with no data cache; despite its name the DC AXI interface provides direct, un-cached access to all peripherals on the associated AXI interconnect.

The CPU High DC interconnect provides high-throughput access to the Tx/Rx packet buffers and off-chip DRAM.

The peripherals on the CPU High peripheral (DP) interconnect include:

| Peripheral | IP Core | Use |

|---|---|---|

| Central DMA | axi_cdma |

DMA controller with access to DRAM and Tx/Rx packet buffers |

| Ethernet | axi_ethernet or ps7_ethernet |

Ethernet MAC |

| Timer | axi_timer |

Timer for periodic interrupts used by MAC scheduled events framework |

| Interrupt Controller | axi_intc |

Configuration interface for interrupt controller |

| UART | axi_uartlie or ps7_uart |

UART transceiver for CPU High stdin/stdout |

| Mailbox | axi_mailbox |

Message FIFO for communicating with CPU Low |

| Mutex | axi_mutex |

Mutual-exclusion status tracking for coordinating packet buffer access with CPU Low |

The CPU High peripheral interconnect is also a master to the shared peripherals interconnect.