5.2. CPU Low and Peripherals¶

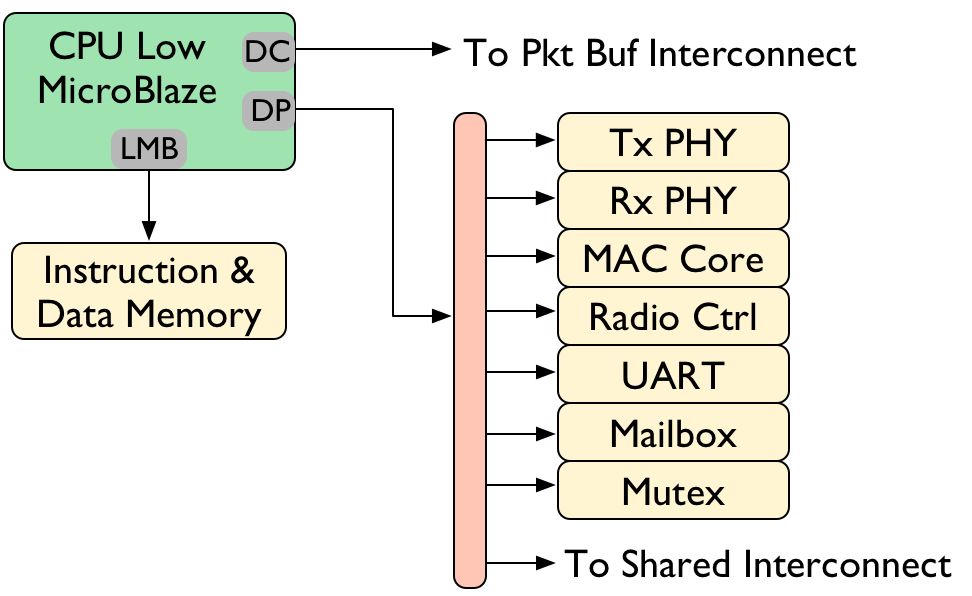

CPU Low is the MicroBlaze CPU dedicated to low-level MAC operations. CPU Low also manages configuration of the Tx/Rx PHY cores and radio interfaces.

The CPU Low MicroBlaze core has two AXI master interfaces:

- DP: Peripheral data interface, 32-bit AXI master

- DC: Cached data interface, 64-bit AXI master

The MicroBlaze is configured with no data cache; despite its name the DC AXI interface provides direct, un-cached access to all peripherals on the associated AXI interconnect.

The peripherals on the CPU Low peripheral (DP) interconnect include:

| Peripheral | IP Core | Use |

|---|---|---|

| Tx PHY | wlan_phy_tx |

Configuration interface for Tx PHY core |

| Rx PHY | wlan_phy_rx |

Configuration interface for Rx PHY core |

| MAC Interface | wlan_mac_hw |

Configuration interface for MAC Interface core |

| UART | axi_uartlite |

UART interface dedicated to CPU Low, optionally configured as stdout |

| Radio Control | wlan_radio_controller |

Utility core to manage real-time state and SPI configuration of radio transceiver |

| Mailbox | axi_mailbox |

Message FIFO for communicating with CPU High |

| Mutex | axi_mutex |

Mutual-exclusion status tracking for coordinating packet buffer access with CPU High |

The CPU Low peripheral interconnect is also a master to the shared peripherals interconnect.