5.3. Inter-CPU Peripherals¶

The two MicroBlaze CPUs (CPU High and CPU Low) share access to a number of peripherals. These shared peripherals enable access to the Tx/Rx Packet Buffers and coordination between the independent programs running in each CPU.

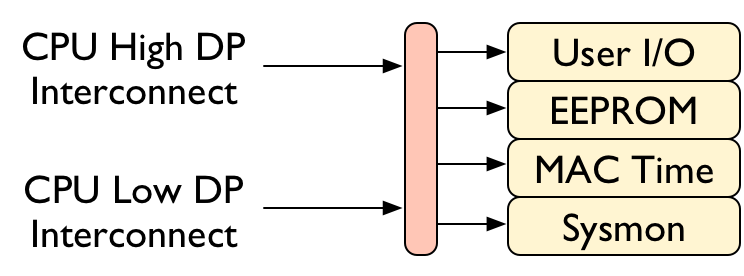

Inter-processor Peripherals¶

The 802.11 MAC software runs in two CPUs. Each CPU runs its own application compiled in the Xilinx SDK. These applications must coordinate their behaviors to realize the overall MAC behavior.

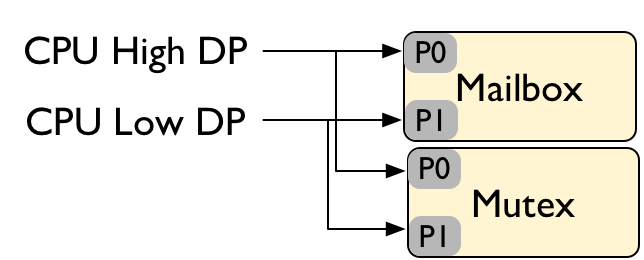

CPU High and CPU Low coordinate by passing messages via a dual-port, bi-directional mailbox. The mailbox (an instance of the Xilinx axi_mailbox IP core) implements two FIFOs, one for each direction of message flow between CPUs.

The mailbox core provides two AXI slave interfaces. The 802.11 FPGA design connects one slave interface to the CPU High peripheral interconnect and one to the CPU Low peripheral interconnect. The AXI slave interfaces operate independently. Both CPUs can read and write mailbox messages simultaneously.

The mailbox core operates as a simple FIFO for 32-bit values. The MAC software framework implements wrappers to construct multi-word message headers and payloads. All mailbox messages use the same header/payload format to ensure consistency in state between CPUs.

The CPUs also use a mutex core (an instance of the Xilinx axi_mutex IP core) to coordinate ownership of Tx/Rx packet buffers.The mutex hardware implements two AXI slave interfaces, one for each CPU. The mutex core implements 32 lockable mutex bits. Either CPU can lock a given mutex bit. Only the CPU which locks a mutex bit can unlock it. Either CPU can query the mutex state to monitor which bits are locked by which CPU.

The MAC software framework assigns one mutex bit to each Tx/Rx packet buffer. The framework uses the mutex to cooridnate runtime ownership of each packet buffer. When one CPU owns the lock on a packet buffer the other CPU must not modify the packet buffer’s contents.

Together the mailbox and mutex enable consistency in packet flow between the MAC software running in the two MicroBlaze CPUs. Refer to the MAC packet flow page for more details.

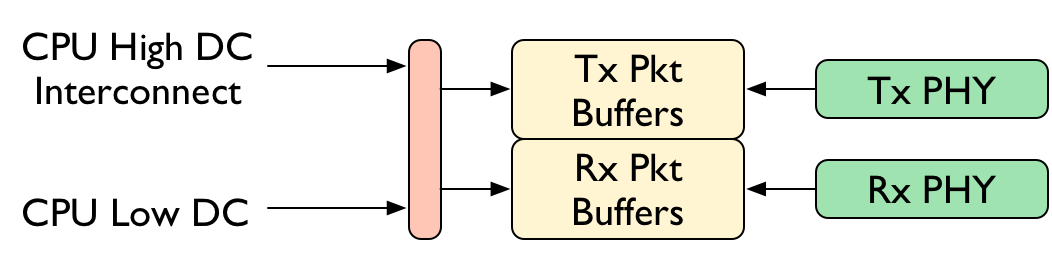

Packet Buffers¶

The Tx and Rx PHY cores connect directly to dedicated packet buffers implemented in on-chip BRAM. Each packet buffer BRAM has two ports. One port is connected directly to the corresponding PHY core. The other port is connected to an AXI interconnect which is mapped into the address space of both CPUs.

Both CPUs have read and write access to the Tx and Rx packet buffers. The MAC framework code implements a strict protocol for accessing packet buffers to avoid inconsistent state between CPU High, CPU Low, and the PHY cores.