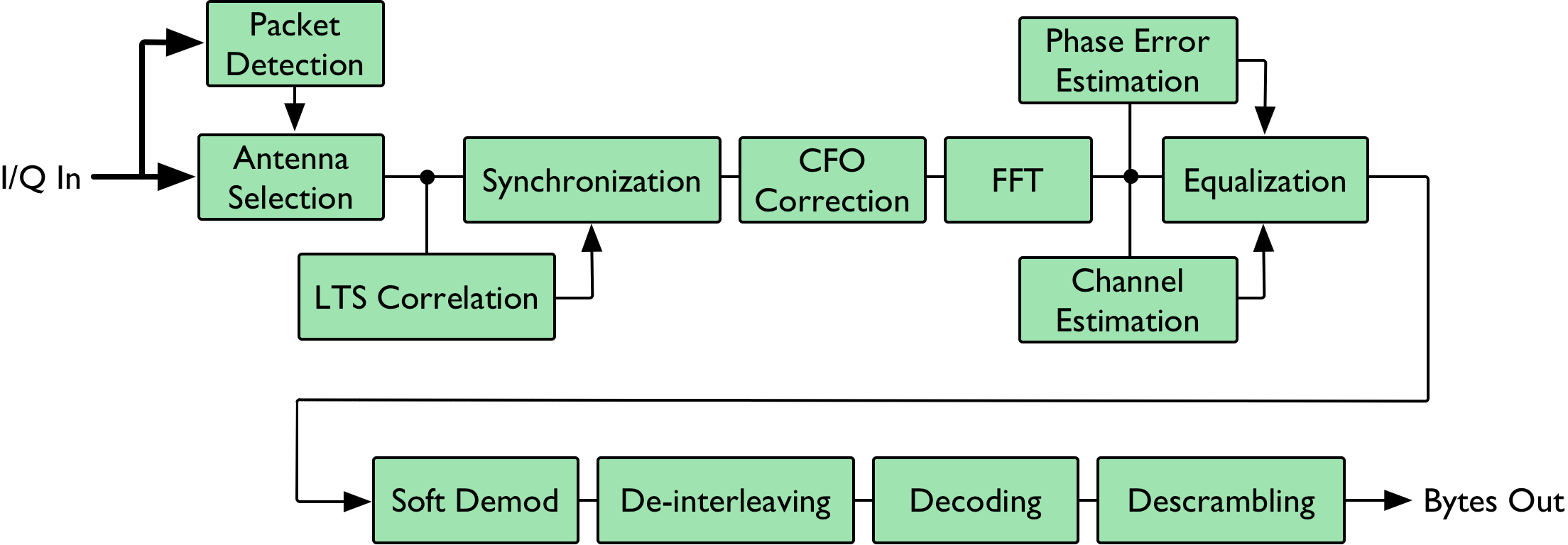

6.2. PHY Receiver¶

The PHY Receiver IP core implements a complete, real-time waveform-to-bytes pipeline in FPGA fabric. The core is implemented in Xilinx System Generator.

Overview¶

The current 802.11 receiver core supports:

- 802.11a/b/g/n waveforms

- DSSS (1-2 Mbps rates)

- NONHT OFDM (all rates)

- HTMF 20MHz OFDM (MCS 0-7)

- Rx sensitivity better than spec

- Detailed logging of every reception

- Sample-accurate timestamp

- Per-subcarrier channel estimates

- CFO estimate