1. 802.11 MAC/PHY Introduction¶

Mango Communications 802.11 MAC/PHY Design implements a real-time 802.11 MAC/PHY in Xilinx FPGAs. The 802.11 design is an ideal starting point for developing programmable wireless systems that interact with standard Wi-Fi devices and to build a custom MAC/PHY based on 802.11.

The Mango 802.11 MAC/PHY design includes custom FPGA IP cores, bare-metal C code, and a Linux driver. Mango provides reference designs which combine these components into ready-to-use designs on commercial hardware.

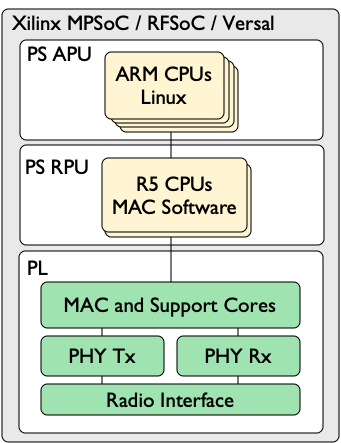

The current reference designs target Xilinx Zynq UltraScale+ MPSoC, RFSoC, and Versal ACAP devices. Mango software and IP cores target the APU, RPU, and PL resources in these Xilinx devices.

1.1. Linux Driver¶

The Mango 802.11 MAC/PHY design includes a Linux driver named mango_wlan. This driver creates wireless network interfaces in Linux running on the same Xilinx SoC as the 802.11 MAC/PHY design. These interfaces are standard Linux wireless NICs that supports the same OS and application interfaces as standard Wi-Fi NICs, but use the Mango 802.11 stack for all MAC/PHY processing. This combination provides complete visibility of the entire wireless networking stack, from the lowest level RF/PHY interface to the top of the application layer. Refer to the Linux Driver section for more details.

Mango reference designs also provide PetaLinux projects which integrate the mango_wlan driver into a bootable Linux design for supported hardware platforms. Refer to the PetaLinux project section for more details.

1.2. MAC Software¶

The 802.11 design implements the full MAC protocol in embedded C code which runs in dedicated CPUs in the FPGA. The MAC software is implemented as bare-metal C applications that run in the R5 CPUs in the RPU of the Xilinx device.

The MAC operates in real time. The MAC software architecture supports both the standard 802.11 MAC and fully custom MAC protocol implementations. All MAC protocol decisions are implemented in the MAC software. The software the configures supporting logic in the FPGA design to achieve the desired timing for over-the-air Tx/Rx interactions.

Refer to the MAC Design section for more details.

1.3. FPGA Design¶

The 802.11 design makes extensive use of the programmable fabric in Xilinx FPGAs. All real-time processing occurs in the fabric, including the Tx/Rx PHY and real-time parts of the MAC. The FPGA fabric is also used to implement interfaces to off-chip components like radio transceivers and other peripherals.

PHY and MAC IP Cores¶

- PHY Transmitter - real-time bytes-to-waveform transmitter

- PHY Receiver - real-time waveform-to-bytes receiver

- MAC Core - real-time building blocks for MAC protocol implementations

Platform Support Cores¶

The PHY and MAC cores are designed to be platform independent. We provide a number of additional cores to implement a fully-functional 802.11 node on reference hardware platforms.

- AD9361 controller - manages AD9361 control interfaces

- User I/O Controller - manages user I/O on FPGA board (LEDs, switches, etc.)

1.4. Licensing¶

The Mango 802.11 MAC/PHY Design is suitable for a wide variety of applications and is available under flexible licensing options.

Please contact Mango Communications with any questions about the design or license options.

License Types¶

The License Type depends on the customer and application.

- Research and Development

- Use and extend source code

- Licensed to single site

- Use for non-profit teaching and research

- No re-distribution

- Product

- Use and extend source code

- Embed and distributed compiled design in products

- Custom

- Tailor license terms for a specific application

- Contact us to discuss your requirements

License Tiers¶

The License Tier depends on what source code access is required.

- MAC Software Source

- Linux kernel driver

- Reference PetaLinux project

- Vitis Embedded workspace with full MAC C source code

- Target supported reference hardware

- FPGA Design Source

- Includes MAC Software source

- Vivado project with IPI design

- Includes source for utility IP cores

- PHY IP cores delivered as netlists

- Target custom hardware

- Full Source

- Includes MAC Software and FPGA Design sources

- Adds source models for PHY IP cores

- Customize and extend Tx/Rx PHY designs