Transmit Controllers¶

The MAC IP Core implements seven independent Transmit Controllers. Each controller implements a flexible finite state machine (FSM) which facilities sequencing transmissions relative to medium activity, reception activity, and other transmit activity. The controllers feed a Tx Arb block which grants use of the Tx PHY and resolves any internal collisions among the controllers.

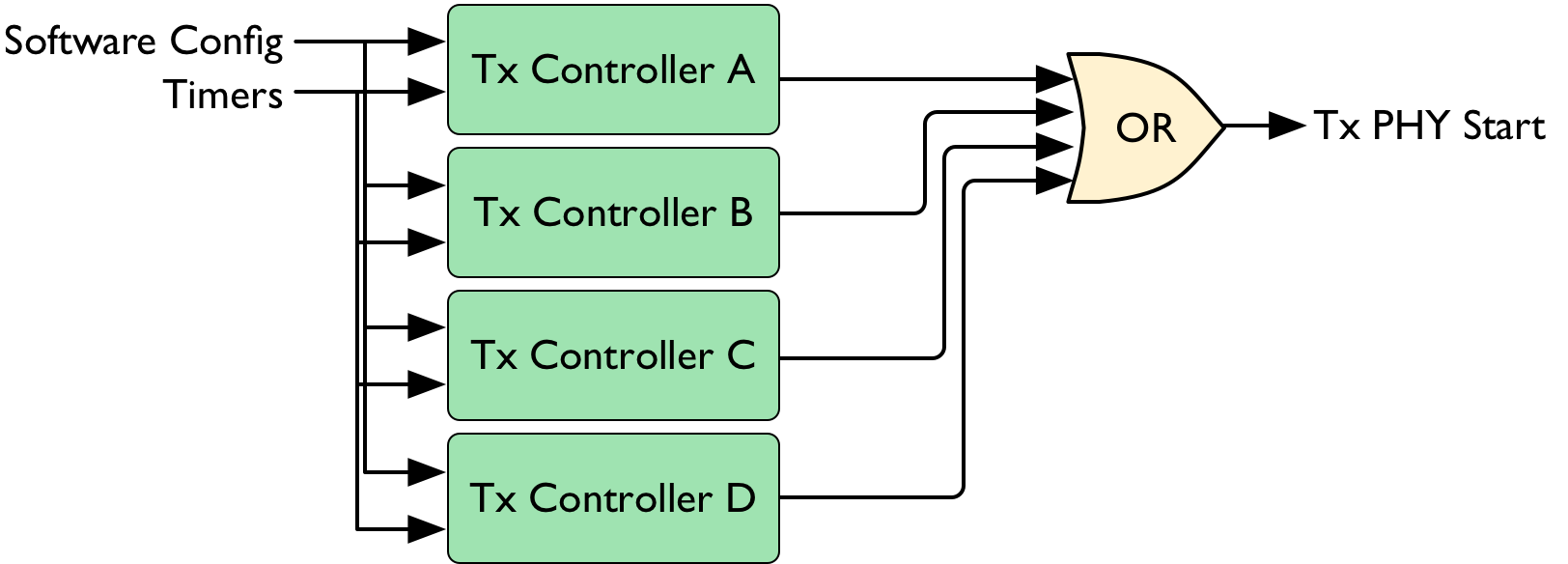

Four Tx Controllers implement the full Tx flow for the EDCA with one controller per Access Class. Each AC controller is configured with MAC timing parameters (AIFSN, Tx priority, etc.) and operate in parallel.

One Tx Controller is dedicated to Beacon transmissions. When this controller is enabled (typically at an AP) it monitors the node’s TSF Timer and schedules a beacon as the next transmission after a TBTT. This behavior is implemented in the MAC core logic ensuring the most accurate timing of beacon transmisions.

The Multicast controller is used for transmitting multicast packets immediately after a beacon transmission, typically as part of the MAC’s DTIM state machine.

The final Tx controller manages control response transmissions such as CTS, ACK, and Block ACK. These response transmissions are managed by the MAC hardwawre ensuring sample-accurate timing of the Tx SIFS and reducing the load on the MAC software.

The behavior of each controller is configured from the MAC software. MAC protocol implementations can use any combination of the Tx controllers.